**OPERATOR'S MANUAL**

**BE-64**

Bus Emulator/Word Generator

Manual Revision 07/10/06 Manual Part Number: BEOM100 Instrument Part Number: BE-64

#### **CERTIFICATION**

Talon Instruments certifies that this product met its published specifications at the time of shipment from the factory.

#### **WARRANTY**

Talon Instruments products are warranted against defects in materials and workmanship as follows:

- (a) One year for the BE-64.

- (b) Ninety days for pod cables.

During the warranty period, Talon Instruments will, at its option, either repair or replace products which prove to be defective.

For warranty service or repair, this product must be returned to the Talon Instruments factory. Buyer shall prepay shipping charges to the factory and Talon Instruments shall pay shipping charges to return the product to the Buyer. However, Buyer shall pay all shipping charges, duties, and taxes for products returned to Talon Instruments from another country.

Talon Instruments warrants that its software and firmware designated by Talon for use with its instruments will execute its programming instructions when properly installed on the instrument. Talon Instruments does not warrant that the operation of the instrument, or software, or firmware will be uninterrupted or error free.

#### LIMITATION OF WARRANTY

The foregoing warranty shall not apply to defects resulting from improper or inadequate maintenance by the Buyer, Buyer-supplied software or interfacing, unauthorized modification or misuse, operation outside of environmental specifications for the product, or improper site preparation or maintenance.

NO OTHER WARRANTY IS EXPRESSED OR IMPLIED. TALON INSTRUMENTS SPE-CIFICALLY DISCLAIMS THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

#### **EXCLUSIVE REMEDIES**

THE REMEDIES PROVIDED HEREIN ARE BUYER'S SOLE AND EXCLUSIVE REMEDIES. TALON INSTRUMENTS SHALL NOT BE LIABLE FOR ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES, WHETHER BASED ON CONTRACT, TORT, OR ANY OTHER LEGAL THEORY.

### **SAFETY FIRST**

# PROTECT YOURSELF AND THE EQUIPMENT. Follow these precautions:

- Don't bypass the VXI chassis' power cord's ground lead with two-wire extension cords or plug adapters.

- Don't disconnect the green and yellow safety-earth-ground wire that connects the ground lug of the VXI chassis power receptacle to the chassis ground terminal.

- Don't energize the VXI chassis until directed to by the installation instructions.

- Don't repair the instrument unless you are a qualified electronics technician and have instructions from Talon Instruments.

- Pay attention to the **WARNING** statements. They point out situations that can cause injury or death.

- Pay attention to the CAUTION statements. They point out situations that can cause equipment damage.

- Use ESD static control procedures when handling the SR192A or any of its modules.

### **Table of Contents**

| 1 | GENERAL     |                                                              |

|---|-------------|--------------------------------------------------------------|

|   | 1.1 Introdu | uction                                                       |

|   | 1.1.1 S     | tandard Features                                             |

|   |             | ignal Overview                                               |

|   |             | Programming Modes                                            |

|   |             | landshaking                                                  |

|   |             | nternal/External Control                                     |

|   |             | tus Structured Interface Simulation                          |

|   |             | Vord Generator Operation                                     |

|   |             | Ion-Bus Structured Interface Simulation1-2                   |

|   | 1.1.10 S    | timulus/Response Testing                                     |

|   | 1.1.11 L    | ogic Recorder1-2                                             |

|   | 1.2 SPEC    | IFICATIONS1-2                                                |

|   | 1.2.1 F     | ield I/O Channels                                            |

|   | 1.2.2 T     | iming                                                        |

|   | 1.3 GENE    | RAL                                                          |

|   |             | CPI Programming                                              |

|   |             | lower on/*RST defaults1-3                                    |

|   |             | XI Interface         1-4           Invironmental         1-4 |

|   |             | ize                                                          |

|   |             | ower1-4                                                      |

|   |             | Cooling Requirements                                         |

|   | 1.4 Techn   | ical Specifications                                          |

|   | 1.4.1 B     | E-64 Timing Set Specifications                               |

|   | 1.4.1       | 1.1 Clock Reference Timing                                   |

|   | 1.4.1       | 1.2 Input Timing Set Signals                                 |

|   | 1.4.2 B     | E-64 Field Channel Specifications1-6                         |

|   | 1.4.2       | 2.1 Non-registered Output Timing                             |

|   | 1.4.2       | 2.2 Registered Output Timing                                 |

|   | 1.4.2       | 2.3 Input Timing                                             |

|   | 1.4.2       | 2.4 Bidirectional Timing                                     |

|   | 1.5 BE-64   | Drive Specifications                                         |

| 2 | PREPARA     | TION                                                         |

|   | 2.1 RECE    | IVING INSPECTION                                             |

|   | 2.1.1 U     | Inpacking Instructions2-1                                    |

|   | 2.1.2 R     | Returning Equipment                                          |

|   | 2.2 PREP    | ARATION FOR STORAGE OR SHIPMENT                              |

|   |             | ackaging2-1                                                  |

|   |             | torage2-1                                                    |

|   | 2.3 PREP    | ARATION FOR USE2-1                                           |

|   |             | ogical Address Selection                                     |

|   | 2.3.2 R     | Rear Panel Connectors                                        |

|   | 2.3.3          | Jumper Configurations                      |      |

|---|----------------|--------------------------------------------|------|

|   | 2.3.4          | Cables                                     |      |

|   |                | TALLATION                                  |      |

|   | 2.4.1          | Initial Power-On                           | 2-4  |

| 3 | OVERVI         |                                            |      |

|   |                | RODUCTION                                  |      |

|   |                | STEM RESOURCES                             |      |

|   |                | NNECTORS AND INDICATORS                    |      |

|   | 3.4 BE-        | 64 FUNCTIONAL OVERVIEW                     | 3-4  |

|   | 3.4.1          | VXI Interface                              |      |

|   | 3.4.2          | Remote Command Language Parser             |      |

|   | 3.4.3<br>3.4.4 | Field Memory and Registers                 |      |

|   |                | 4.4.1 Field Register Settings              |      |

|   | 3.4            | 3.4.4.1.1 Field Direction                  |      |

|   |                | 3.4.4.1.2 Output Mode                      |      |

|   |                | •                                          |      |

|   | 2              | 3.4.4.1.3 Input mode                       |      |

|   | 3.4            |                                            |      |

|   |                | 3.4.4.2.1 Timing Set TSOUT Signals         |      |

|   |                | 3.4.4.2.2 Timing Set Field Control Signals |      |

|   |                | 3.4.4.2.3 Timing Set Probe Signals         |      |

|   | 0.45           | 3.4.4.2.4 Timing Set Test/Delay Options    |      |

|   | 3.4.5          | Sequence Control                           |      |

|   |                | 4.5.1 Idle Sequence                        |      |

|   | -              | 4.5.2 Sequence Initiation                  |      |

|   |                | 4.5.3 Sequence Looping                     |      |

|   |                | 4.5.4 UUT Bus Acquisition Operation        |      |

|   | 3.4.6          |                                            |      |

|   |                | 4.6.1 PIO1/PIO2                            |      |

|   | 3.4            | 4.6.2 OUT0-7                               |      |

|   | 3.4.7          | Byte Enable Memory                         |      |

|   |                | SYNC                                       | 3-14 |

| 4 | OPERA1         |                                            |      |

|   |                | RODUCTION                                  |      |

|   | 4.2 SCF        | PI CONVENTIONS                             | 4-1  |

|   | 4.2.1          | SCPI Command Structure                     | 4-1  |

|   | 4.             | 2.1.1 Program Header Definition            | 4-1  |

|   |                | 4.2.1.1.1 Common Command Header            |      |

|   |                | 4.2.1.1.2 Instrument Control Header        | 4-1  |

|   | 4.:            | 2.1.2 Parameter List Definition            | 4-2  |

|   | 4.3 BUS        | S EMULATION TUTORIAL                       | 4-2  |

|   | 4.3.1          | Word Generator View                        | 4-2  |

|   | 4.3.2          | Bus Emulation Overview                     | 4-4  |

|   | 4.4 PR         | OGRAMMING EXAMPLES                         | 4-6  |

|   | 441            | Programming the Timing Memory              | 4-7  |

|     | 4.4.1.1   | Programming The Timing Setup Data           | 4-8  |

|-----|-----------|---------------------------------------------|------|

|     | 4.4.1.    | 1.1 Programming the Clock Source            | 4-8  |

|     | 4.4.1.    | 1.2 Programming the Delay Count             | 4-9  |

|     | 4.4.1.    | 1.3 Programming the Timeout Count           | 4-9  |

|     | 4.4.1.2   | Defining A Timing Set                       | 4-9  |

|     | 4.4.1.3   | Programming the Timing Memory               | 4-10 |

|     |           | 3.1 Programming the Field Control Registers |      |

|     | 4.4.1.    | 3.2 Programming the Timing Cells            | 4-13 |

|     |           | 3.3 Programming the Handshake Tests         |      |

|     |           | amming The Table Field Memory               |      |

|     |           | uting a Timing Cycle                        |      |

|     |           | uting a Sequence                            |      |

|     | J         | amming the Byte Enable (BEN) Memory         |      |

| 4.4 |           | amming SYNC                                 |      |

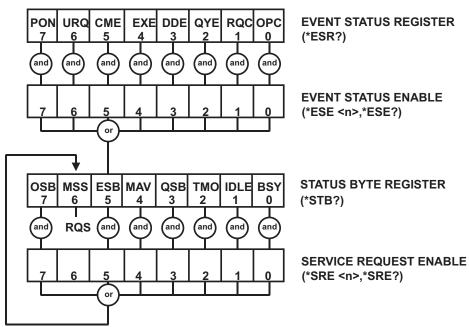

| 4.5 | BE-64 Sta | tus/Event Reporting Structures              | 4-19 |

|     |           | SCRIPTION                                   |      |

|     |           | CTION                                       |      |

| 5.2 | PARAMET   | TER LIST CONVENTIONS                        | 5-1  |

|     |           | meter List Definition                       |      |

|     |           | meter List Symbols                          |      |

| 5.2 |           | meter List Keywords                         |      |

| F ( | 5.2.3.1   | Parameter Types Keywords                    |      |

|     |           | ts and Queries                              |      |

|     |           | SUBSYSTEM                                   |      |

|     |           | ?                                           |      |

|     |           | Mpare?                                      |      |

|     |           | SUBSYSTEM                                   |      |

|     |           | ing]                                        |      |

|     | -         | uence                                       |      |

| 5.4 | 4.3 :FUN  | Ction                                       | 5-7  |

|     | 5.4.3.1   | :BUS                                        | 5-7  |

|     | 5.4.3.2   | EXECute:FUNCtion:BRAM?                      |      |

|     | 5.4.3.3   | EXECute:FUNCtion:EEPRom?                    |      |

|     | 5.4.3.4   | EXECute:FUNCtion:FLASh?                     |      |

|     | 5.4.3.5   | :ROM                                        |      |

|     | 5.4.3.6   | :RAM                                        |      |

|     |           | Τh                                          |      |

|     |           | d                                           |      |

|     |           | UBSYSTEM                                    |      |

|     |           | et                                          |      |

|     |           | et                                          |      |

|     |           | Trg                                         |      |

|     | 5.5.3.1   | [:STATe]                                    |      |

|     | 5532      | ·SOURce                                     | 5-15 |

| 5.5.4 :   | :FIELd           | 5-16 |

|-----------|------------------|------|

| 5.5.      | 6.4.1 :MODE      | 5-16 |

| 5.5.5 :   | :BENable         | 5-17 |

| 5.5.      | i.5.1 [:STATe]   | 5-17 |

| 5.5.      | 5.5.2 :DATA      | 5-18 |

| 5.5.6 :   | :SYNC            | 5-18 |

| 5.5.      | i.6.1 [:STATe]   | 5-18 |

| 5.5.      | 6.6.2 :POSition  | 5-19 |

| 5.5.      | 6.6.3 :LOOP      | 5-19 |

| 5.6 STAT  | Tus SUBSYSTEM    | 5-21 |

| 5.6.1 :   | :OPERation       | 5-21 |

| 5.6.      | i.1.1 [:EVENt]   | 5-21 |

| 5.6.      | 5.1.2 :CONDition | 5-21 |

| 5.6.      | i.1.3 :ENABle    | 5-21 |

| 5.6.2 :   | :QUEStionable    | 5-21 |

| 5.6.      | .2.1 [:EVENt]    | 5-21 |

| 5.6.      | 5.2.2 :CONDition | 5-21 |

| 5.6.      | i.2.3 :ENABle    | 5-21 |

| 5.6.3 :   | :PRESet          | 5-21 |

| 5.7 SYST  | Tem SUBSYSTEM    | 5-22 |

| 5.7.1 :   | :ERRor           | 5-22 |

| 5.7.2 :   | :VERSion         | 5-22 |

| 5.8 TABL  | LE SUBSYSTEM     | 5-23 |

|           | :DEFine          |      |

| _         | [:DATA]          |      |

|           | :WORD:<br>:FIELd |      |

| 5.8.      |                  |      |

| 5.8.      |                  |      |

| 5.8.      |                  |      |

|           | .4.4 :CHANnel    |      |

| 5.8.      |                  |      |

| 5.8.      |                  |      |

| 5.8.5 :   | :DELete          | 5-30 |

| 5.8.      |                  |      |

| 5.8.      |                  | 5-31 |

| 5.8.6 :   | :BENable         | 5-31 |

|           | :DIRectory       |      |

| 5.8.8 :   | :FREE            | 5-32 |

| 5.9 TIMin | ng SUBSYSTEM     | 5-33 |

|           | :DEFine          |      |

|           | :SETup           |      |

| 5.9.      |                  |      |

|           | 0.2.2 CTIMeout   |      |

| 5.9.      | 0.2.3 :DELay     | 5-35 |

| 5.9.3<br>5.9.4 | -       | [A]                                                 |     |

|----------------|---------|-----------------------------------------------------|-----|

| 5.9.4          | 5.9.4.1 | :DIRection                                          |     |

|                | 5.9.4.1 | :OREGister                                          |     |

|                | 5.9.4.2 | :OCONtrol                                           |     |

|                | 5.9.4.3 | :ISTRobe                                            |     |

| F 0 F          |         |                                                     |     |

| 5.9.5<br>5.9.6 |         |                                                     |     |

| 0.0.0          | 5.9.6.1 | :DELay                                              |     |

|                | 5.9.6.2 | :LEVel                                              |     |

|                | 5.9.6.3 | :STRobe                                             |     |

|                | 5.9.6.4 | :RESet                                              |     |

| 597            |         | ete                                                 |     |

| 0.0.7          | 5.9.7.1 | [:NAME]                                             |     |

|                | 5.9.7.2 | :ALL                                                |     |

| 5.9.8          |         | ctory                                               |     |

| 0.0.0          |         | COMMANDS                                            |     |

|                |         | - Clear Status (section 10.3)                       |     |

|                |         | - Event Status Enable Command (section 10.10)       |     |

|                |         | ? - Event Status Enable Query (section 10.11)5-4    |     |

| 5.10           |         | ? - Event Status Register Query (section 10.12)     |     |

|                |         | ? - Identification Query (section 10.14)            |     |

|                |         | - Operation Complete Command (section 10.18)        |     |

|                |         | - Reset Command (section 10.32)                     |     |

|                |         | - Service Request Enable Command (section 10.34)    |     |

|                |         | ? - Service Request Enable Query (section 10.35)5-4 |     |

|                |         | ? - Read Status Byte Query (section 10.36)          |     |

|                |         | ? - Self-Test Query (section 10.38)                 |     |

|                |         | EL INTERFACE COMMANDS                               |     |

|                |         | - Asynchronous Mode Control                         |     |

|                |         | P - Abort Normal Operation                          |     |

|                |         | P - Begin Normal Operation                          |     |

|                |         | - Control Event                                     |     |

|                |         | Clear                                               |     |

|                |         | P - End Normal Operation                            |     |

|                |         | Read Protocol Error5-4                              |     |

|                |         | 3 - Read Status Byte                                |     |

|                |         | so                                                  | CPI |

| BEGINNE        |         |                                                     |     |

|                |         | CTION                                               |     |

|                |         | ERS                                                 |     |

|                |         |                                                     |     |

|                |         | CTUATION and SYNTAX                                 |     |

|                |         | SED RULES: A-3                                      |     |

| 6 T            | EXT SYM | MBOLS                                               | 3   |

| 7 CY                   | CLE and DATA TABLE NAMES        | A-4   |

|------------------------|---------------------------------|-------|

|                        | В                               | COM-  |

| MAND DES               |                                 |       |

|                        | PI CONFORMANCE                  |       |

|                        | PI COMMAND SUMMARY              |       |

| 3 SCI                  | PI MANDATED COMMANDS            | B-2   |

| 4 IEE                  | E COMMON COMMANDS               | B-2   |

| 5 LO\                  | W LEVEL INTERFACE COMMANDS      | B-3   |

| APPENDIX<br>TO BUS EM  | C MULATION                      | GUIDE |

| 1 INT                  | RODUCTION                       | C-1   |

| 2 WO                   | ORD GENERATOR OVERVIEW          | C-1   |

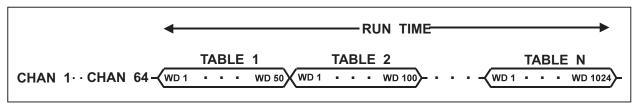

| 2.1                    | Tables                          | C-2   |

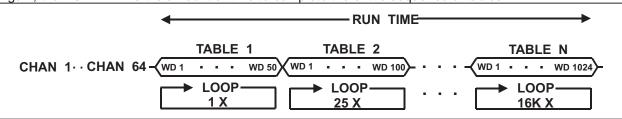

| 2.2                    | Table Looping                   |       |

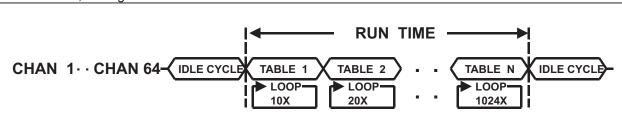

| 2.3                    | Idle Cycle                      | C-2   |

| 3 BUS                  | S EMULATION OVERVIEW            | C-3   |

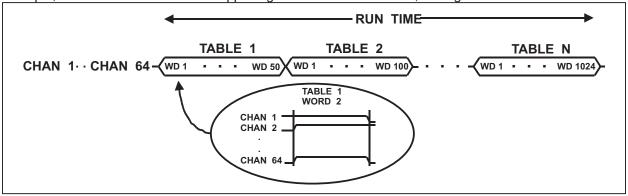

| 3.1                    | Fields                          | C-3   |

| 3.2                    | Field Timing                    |       |

| 3.3                    | Timing Signals                  |       |

| 4 BUS                  | S EMULATION TESTING             | C-6   |

| APPENDIX<br>A16/A24 RE | D<br>EGISTERS                   | BE-64 |

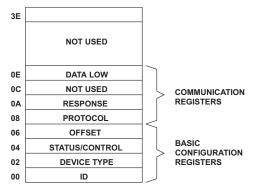

| 1 INT                  | RODUCTION                       | D-1   |

| 2 A16                  | 6 MEMORY                        | D-1   |

| 3 A24                  | 1 MEMORY                        | D-2   |

| 3.1                    | Timing Memory Format            | D-3   |

| 3.2                    | Field Memory Format             |       |

| APPENDIX               | E                               | CABLE |

| DESIGN EX              | KAMPLES                         |       |

|                        | <u>F.</u>                       |       |

| WORKSHE                |                                 |       |

| APPENDIX<br>NAL DESCI  | G                               | SIG-  |

|                        |                                 | 0.4   |

|                        | OGRAM I/O                       |       |

| 1.1<br>1.2             | PIO DATA LINES                  |       |

|                        | PIO CONTROL LINES               |       |

|                        | UNTER OUTPUT                    |       |

| 2.1                    | OUT DATA LINES                  |       |

| 2.2                    | OUT CONTROL LINES               |       |

|                        | MING SET SIGNALS                |       |

| 3.1                    | Timing Set Output Signals       |       |

| 3.2<br>3.3             | Timing Set Test Signals         |       |

| 3.3<br>3.4             | Timing Set Probe Signals        |       |

| 3.5                    | Timing Set Nisc Control Signals |       |

| 3.6                    | Bus Arbitration Signals         |       |

| 3.7                    | Timing Set External Clock       | G-4   |

| 3.8                    | Timing Set SYNC                 | G-4   |

| 4 PRO | OPRIETARY CONTROL SIGNALS      | G-4 |

|-------|--------------------------------|-----|

| 4.1   | External Sequence Stop Control |     |

| 4.2   | Sequence State Output Signals  | G-4 |

| 5 FIE | LD CONTROL SIGNALS             | G-5 |

| 5.1   | Field Signals                  | G-5 |

| 5.2   | Byte Enable Signals            |     |

| 5.3   | Bus Emulator Output Clock      |     |

| 6 VXI | TTL TRIGGER SIGNALS            | G-6 |

| 6.1   | TTL Trigger Source Selection   | G-6 |

| 6.2   | TTL Trigger Output Selection   |     |

| 7 SEL | _F TEST FIXTURE SIGNALS        | G-6 |

| 7.1   | Self Test Input Signal         | G-6 |

| 7.2   | Self Test Output Signals       | G-6 |

| 8 MIS | CELLANEOUS SIGNALS             | G-6 |

| 8.1   | Reset Signal                   | G-6 |

| 8.2   | UUT Power On Signal            | G-6 |

| 8.3   | Power Lines From VXI Backplane | G-6 |

|       | HBE-64 ACCESS                  | IM- |

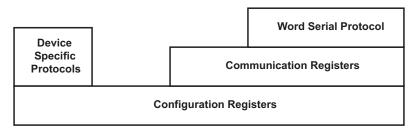

| 1 VXI | COMMUNICATION LAYERS           | H-1 |

| 1.1   | Register Based Devices         | H-1 |

| 1.2   | Message Based Devices          |     |

| 2 THE | WORD SERIAL PROTOCOL           | H-1 |

| 2.1   | The Word Serial Bottleneck     | H-2 |

| 3 SPF | FEDING UP TABLE TRANSFERS      | H-2 |

# **List of Figures**

| FIGURE 1-1 TSCLK-A IN REFERENCE TO EXCLK              | 1-5  |

|-------------------------------------------------------|------|

| FIGURE 1-2 INPUT TIMING SET SIGNALS                   | 1-6  |

| FIGURE 1-3 TSOUT(1-8) SIGNALS WITH RESPECT TO TSCLK-A | 1-6  |

| FIGURE 1-4 DATA VALID/INVALID, INTERNALLY ENABLED     | 1-7  |

| FIGURE 1-5 DATA VALID, CONTINUOUSLY ENABLED           |      |

| FIGURE 1-6 DATA VALID/INVALID, INTERNALLY ENABLED     | 1-8  |

| FIGURE 1-7 DATA VALID/INVALID, EXTERNALLY ENABLED     | 1-8  |

| FIGURE 1-8 DATA VALID, EXTERNALLY STROBED             | 1-9  |

| FIGURE 1-9 DATA VALID, INTERNALLY STROBED             | 1-9  |

| FIGURE 1-10 EXTERNAL DIRECTION TO INPUT               | 1-10 |

| FIGURE 1-11 DATA SET-UP AND HOLD, INTERNALLY STROBED  | 1-10 |

| FIGURE 1-12 DATA SET-UP AND HOLD, EXTERNALLY STROBED  | 1-11 |

| FIGURE 1-13 EXTERNAL DIRECTION SET TO OUTPUT          | 1-11 |

| FIGURE 2-1 REAR PANEL                                 | 2-2  |

| FIGURE 2-2 LOCATION OF JUMPER POINTS (BOTTOM BOARD)   | 2-3  |

| FIGURE 3-1 BE-64 COMPLETE BLOCK DIAGRAM               | 3-2  |

| FIGURE 3-2 FRONT PANEL CONNECTORS AND INDICATORS      | 3-3  |

| FIGURE 3-3 SIMPLIFIED BLOCK DIAGRAM                   | 3-4  |

| FIGURE 3-4 FIELD MEMORY/REGISTER BLOCK DIAGRAM        | 3-5  |

| FIGURE 3-5 TIMING MEMORY BLOCK DIAGRAM                | 3-6  |

| FIGURE 3-6 TIMING SET SIGNALS                         | 3-8  |

| FIGURE 3-7 SEQUENCE CONTROL BLOCK DIAGRAM             | 3-10 |

| FIGURE 3-8 SEQUENCE OVERVIEW                          | 3-11 |

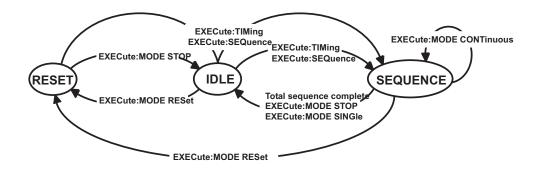

| FIGURE 3-9 SEQUENCE STATE DIAGRAM                     | 3-12 |

| FIGURE 3-10 DMA STATE DIAGRAM                         | 3-12 |

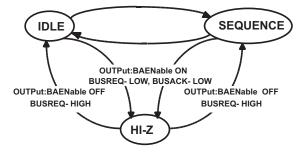

| FIGURE 3-11 PROGRAMMED I/O BLOCK DIAGRAM              |      |

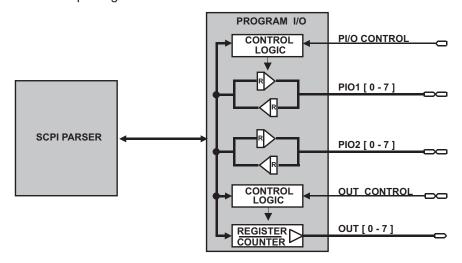

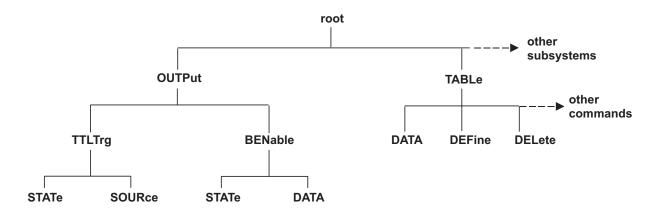

| FIGURE 4-1 SCPI TREE-LIKE STRUCTURE                   | 4-2  |

| FIGURE 4-2 SIMPLIFIED WORD GENERATOR VIEW             | 4-3  |

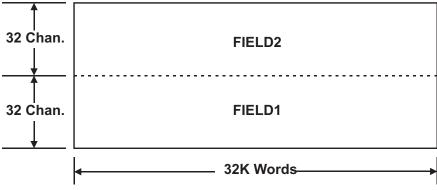

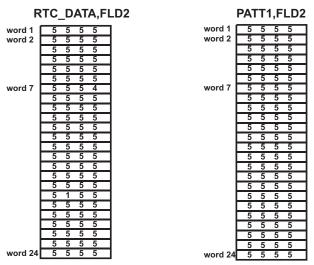

| FIGURE 4-3 FIELD MEMORY TABLES                        |      |

| FIGURE 4-4 WORD GENERATOR VIEW                        |      |

| FIGURE 4-5 TABLE LOOPING                              | 4-4  |

| FIGURE 4-6 IDLE CYCLE                                 | 4-4  |

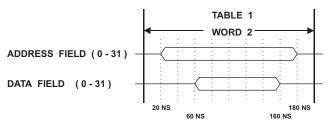

| FIGURE 4-7 TABLE WORD EXAMPLE CLOSE-UP                | 4-4  |

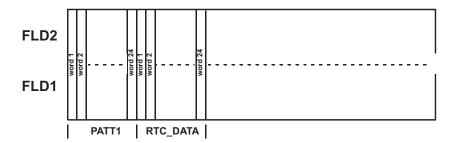

| FIGURE 4-8 BUS CYCLE FIELDS                           |      |

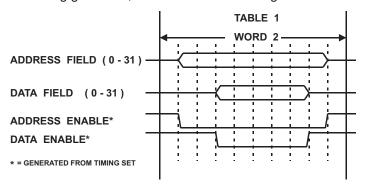

| FIGURE 4-9 BUS CYCLE FIELD TIMING                     | 4-5  |

| FIGURE 4-10 TABLE WORD TIMING BUS CYCLE               | 4-5  |

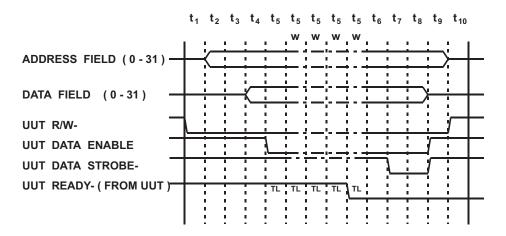

| FIGURE 4-11 HANDSHAKE EXAMPLE                         | 4-6  |

| FIGURE 4-12 TIMING SET                                |      |

| FIGURE 4-13 SAMPLE UUT BLOCK DIAGRAM                  |      |

| FIGURE 4-14 TIMING MEMORY                             |      |

| FIGURE 4-15 FIELD CONTROL PROGRAMMING                 | 4-10 |

| FIGURE 4-16 IDLE TIMING SET FIELD SETTINGS            | 4-11 |

| FIGURE 4-17 WRITE_MEM TIMING SET FIELD SETTINGS | 4-12 |

|-------------------------------------------------|------|

| FIGURE 4-18 READ_MEM TIMING SET FIELD SETTINGS  |      |

| FIGURE 4-19 FIELD MEMORY TABLES                 |      |

| FIGURE 4-20 FIELD MEMORY ALLOCATION             | 4-15 |

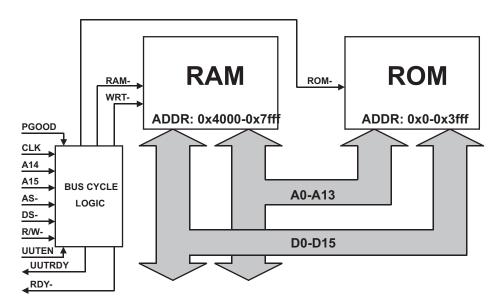

| FIGURE 4-21 UUT PIO/BEN EXAMPLE                 | 4-17 |

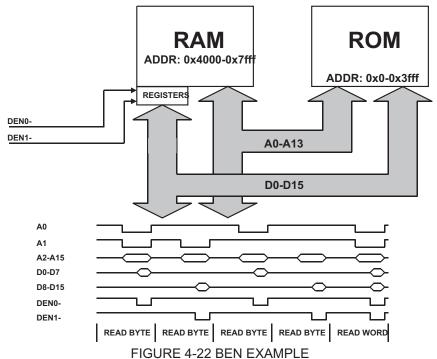

| FIGURE 4-22 BEN EXAMPLE                         | 4-18 |

| FIGURE 4-23 STATUS REPORTING REGISTERS          | 4-19 |

| FIGURE 5-1 CALCulate:TCOMpare? Example          | 5-5  |

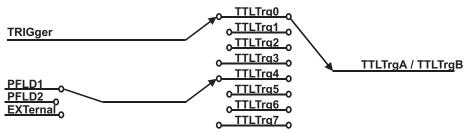

| FIGURE 5-2 TTLTRG:SOURce CHOICES                | 5-16 |

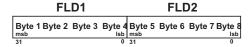

| FIGURE 5-3 BEN DATA FORMAT                      | 5-18 |

| FIGURE 5-4 :DEFine EXAMPLE                      | 5-24 |

| FIGURE 5-5 TABLE DATA BLOCK FORMAT              | 5-24 |

| FIGURE 5-6 TABLE AFTER :CHANnel COMMAND         | 5-28 |

| FIGURE 5-7 TABLE BEFORE :CEXPand                | 5-29 |

| FIGURE 5-8 TABLE AFTER :CEXPand COMMAND         | 5-29 |

| FIGURE 5-9 :FILL EXAMPLE                        |      |

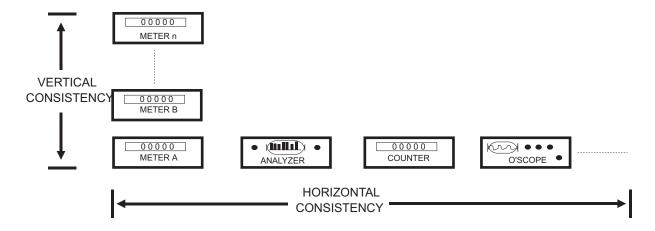

| FIGURE A-1 COMMAND CONSISTENCY                  |      |

| FIGURE A-2 SAME KEYWORDS IN DIFFERENT SUBSYSTEM | A-2  |

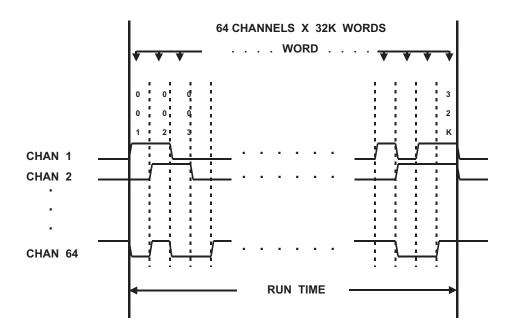

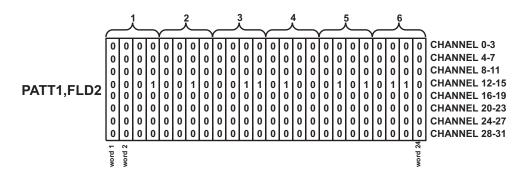

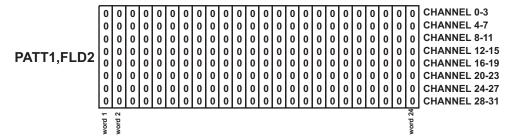

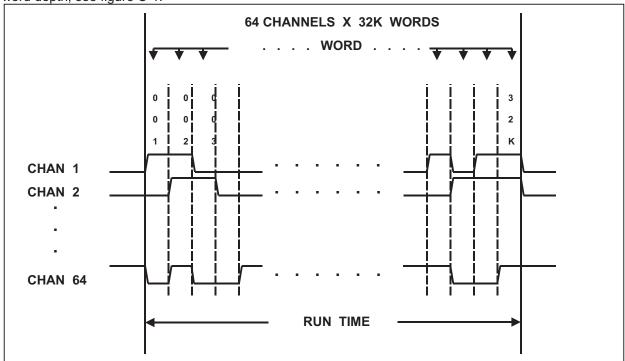

| FIGURE C-1 64 CHANNELS BY 32K WORDS             | C-1  |

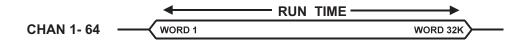

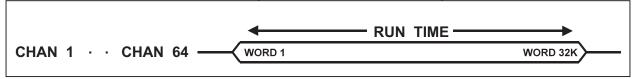

| FIGURE C-2 TABLES                               |      |

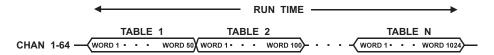

| FIGURE C-3 TABLE LOOPING                        | C-2  |

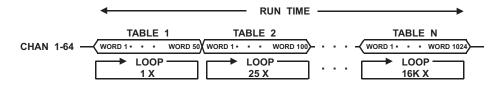

| FIGURE C-4 IDLE CYCLE INCLUDED                  | C-2  |

| FIGURE C-5 64 CHANNELS CONSOLIDATED             | C-2  |

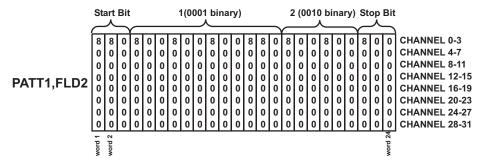

| FIGURE C-6 "INSIDE" EACH WORD                   | C-3  |

| FIGURE C-7 WORD DIVIDED INTO TIMING INCREMENTS  |      |

| FIGURE C-8 IMPROVED BUS STRUCTURE               | C-4  |

| FIGURE C-9 FIELD TIMING SIGNALS                 |      |

| FIGURE C-10 BUS STRUCTURE WITH FIELDS           | C-4  |

| FIGURE C-11 "BUS CYCLE" TIMING SIGNALS          | C-5  |

| FIGURE C-12 TEST CONDITION AND "WAIT" STATE     |      |

| FIGURE C-13 SAMPLE UUT INTERFACE                | C-6  |

| FIGURE D-1 A16 REGISTER MAP                     | D-1  |

| FIGURE D-2 A24 MEMORY MAP                       | D-3  |

| FIGURE H-1 VXI COMMUNICATION LAYERS             | H-1  |

| FIGURE H-2 BYTE TRANSFER PROTOCOL EXAMPLE       | H-2  |

### **List of Tables**

| TABLE 2-1 BOTTOM BOARD REV A AND (REV NC) JUMPER SETTINGS | 2-3  |

|-----------------------------------------------------------|------|

| TABLE 4-1 PRE-DEFINED TIMING SET NAMES                    | 4-9  |

| TABLE 4-2 FIELD DIRECTION/SELECTION CHOICES               | 4-11 |

### 1 GENERAL

#### 1.1 Introduction

The BE-64 houses the digital resources required in digital test and trouble-shooting applications. The BE-64 may be software configured to handle applications ranging from basic word generation to sophisticated microprocessor or bus emulation. See Appendix C for information on bus emulation.

#### 1.1.1 Standard Features

The Talon BE-64 is a single slot "C" size, VXI module. The BE-64 adheres to the SCPI (Standard Commands for Programmable Instruments) remote programming format version 1991.0.

#### 1.1.2 Signal Overview

- 64 I/O channels x 32K bits/channel (Address and Data fields or Word Generator Data; maximum data rate = 25 MHz)

- 12 Output Programmable Timing and Control Signals; maximum output rate = 50 MHz

- 3 Input Programmable Timing and Control Signals; maximum input rate = 50 MHz

- 6 Input External Field Control Signals; maximum input rate = 25 MHz

- 24 Programmed Input/Output Signals; data rate defined by data transfer rate of VXI controller. 16 input/output, 8 output/counter.

- 30 miscellaneous timing and control signals required for exact simulation of various microprocessors and compatible signals for parallel to serial word generator converter pod.

- 2 Clock Outputs; frequency = 10 MHz, 20 MHz, or 50 MHz

- 1 Clock Input; maximum frequency = 50 MHz

- All signals TTL compatible.

#### 1.1.3 Programming Modes

The BE-64 can be programmed to operate in either single cycle or continuous cycle mode. Continuous cycle mode allows for easier trouble-shooting of the Unit Under Test (UUT).

#### 1.1.4 Handshaking

Since most digital buses require some form of input control, the BE-64 has the capability to handshake with the UUT. One edge sensitive input and two level sensitive inputs are provided for this function.

#### 1.1.5 Internal/External Control

The Timing Sets of the BE-64 can be internally or externally clocked (DC to 50 MHz). The internal clock can be software configured to 10 MHz, 20 MHz, or 50 MHz.

The direction, enable and strobe lines of the 64 I/O channels can also be internally or externally controlled.

#### 1.1.6 Microprocessor Bus Emulation

The BE-64 can be programmed to simulate the bus structured interface of any microprocessor incorporating an address and data bus, each bus not exceeding 32 bits in width. All timing and control signals are simulated, generating bus cycles to 50 MHz.

#### 1.1.7 Bus Structured Interface Simulation

Bus structured interfaces are simulated exactly like the bus structured interface of a microprocessor. The architecture of the BE-64 has enabled Talon customers to simulate well over 1000 different digital interfaces. These interfaces range from a serial communication interface to a high speed VME bus structured interface. Talon offers "set up" configurations for several bus structured interfaces including the ones listed below. Contact the factory for availability of other configurations not listed..

VME bus AT bus VXI bus

#### 1.1.8 Word Generator Operation

The word generator operation of the BE-64 incorporates the following features:

- 64 I/O channels x 32K bits/channel; 25 MHz data rates; Tristate Output control

- 32 I/O channels x 64K bits/channel; 50MHz data rates (external adapter required).

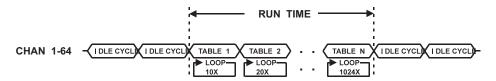

- The 32K memories are software allocated into tables. Up to 256 tables may be defined.

- Table length is programmed from 1 word to 32K words.

- Each table may be looped from 1 to 64K times, or run in continuous mode.

- Up to 16 table / timing entries can be sequenced together, generating zero clocks between tables.

- Continuous operation of an "idle" cycle which can run while downloading new data tables and/or sequences.

- Each table can be input or output.

#### 1.1.9 Non-Bus Structured Interface Simulation

The BE-64 word generator mode allows the simulation of almost any user defined digital interface.

#### 1.1.10 Stimulus/Response Testing

For test applications where test vectors are available, the BE-64 can be programmed to transmit or receive 64 channels by 32K bits per channel at frequencies to 25 MHz.

#### 1.1.11 Logic Recorder

The BE-64 can be programmed to record up to 64 channels by 32K/channel. When used in conjunction with Talon's serial word generator card, 2 megabits of serial data can be recorded.

#### 1.2 SPECIFICATIONS

#### 1.2.1 Field I/O Channels

| General                                                   |                                                      |

|-----------------------------------------------------------|------------------------------------------------------|

| Number of Channels:  Memory Depth:                        | 64 Bidirectional32K bits per channel                 |

| Timing                                                    |                                                      |

| Data Rate Falltime Skew I/O Pins Rise time                |                                                      |

| Output Levels                                             |                                                      |

| High, open<br>Low, open<br>High, sourcing<br>Low, sinking | 3.4V min.<br>0.4V max.<br>12ma @ 3.4V<br>24ma @ 0.4V |

| Input Levels                                              |                                                      |

| High                                                      |                                                      |

| E     | ternal Tri-state Control Input Levels Disabled, High Enabled, Low                           |                         |

|-------|---------------------------------------------------------------------------------------------|-------------------------|

| 1.2.2 | Timing                                                                                      |                         |

| Ti    | nebase                                                                                      |                         |

|       | Subcycle/Cell Period Min                                                                    | 100ns x 215 or external |

| E     | ternal Clock                                                                                |                         |

|       | Max. Speed                                                                                  | 8ns                     |

| Co    | ntrol Timing Generator                                                                      |                         |

|       | Control Outputs Resolution Min. Pulse Width Typical Rise time Typical Falltime Typical Skew |                         |

| Tr    | gger Timing                                                                                 | ,                       |

|       | Min. Pulse Width Level Trigger Edge Trigger Min. between Trigs                              | 10ns                    |

#### 1.3 GENERAL

**Delay Timing**

#### 1.3.1 SCPI Programming

Conforms to SCPI Version 1991.0 and IEEE-488.2 standard mandated commands. Root level commands include:

TABLe TIMing EXECute OUTPut CALCulate STATus

SYSTem

#### 1.3.2 Power on/\*RST defaults

The following table lists the power on/\*RST defaults of the BE-64.

The \*TST? command sets the BE-64 to the power on defaults after completion of the self test.

| SUBSYSTEM          | DEFAULT                                                                         |  |

|--------------------|---------------------------------------------------------------------------------|--|

| TABLe              | No tables defined.                                                              |  |

| TIMing             | Pre-defined timing sets set to two cells. All user defined timing sets deleted. |  |

| SETup:CLOCk        | 10                                                                              |  |

| SETup:DELay        | 0                                                                               |  |

| SETup: CTIM eout   | 0                                                                               |  |

| FCONtrol:DIRection | OUTPut                                                                          |  |

| FCONtrol:OREGister | OFF                                                                             |  |

| FCONtrol:OCONtrol  | INTernal                                                                        |  |

| CELL               | All cells set to #Hffff.                                                        |  |

| TEST               | All test cells reset.                                                           |  |

| SUBSYSTEM                 | DEFAULT                            |

|---------------------------|------------------------------------|

| EXECute                   |                                    |

| MODE                      | RESet                              |

| FIELd                     | OUT,0                              |

| OUTPut                    |                                    |

| FIELd:MODE PIO1/PIO2      | INPut                              |

| FIELd:MODE OUT            | OUTPut                             |

| TTLTrg <n>:STATe</n>      | OFF                                |

| TTLTrg <n>:SOURce</n>     | TTLTrg0 - TRIGGER, TTLTrg4 - PFLD1 |

| TTLTrg <a b>:STATe</a b>  | OFF                                |

| TTLTrg <a b>:SOURce</a b> | TTLTrg0                            |

| BENable: STATe            | OFF                                |

| BENable: DATA             | All codes set to zero.             |

| BAENable                  | OFF                                |

| RESet                     | HIGH                               |

The Event status and Service Request enable registers are set to zero on power-up only.

#### 1.3.3 VXI Interface

Message based, 1K byte input buffer. Supports the following subsets/protocols:

- A24 A16 D16 Slave;

- VXIbus IEEE-488.2 Instrument Protocol (I4);

- VXIbus Event Generation Protocol (EG);

- VXIbus Interrupter.

- SC (Static Configuration) Device;

- DC (Dynamic Configuration) Device;

#### 1.3.4 Environmental

#### **Temperature Range**

#### Altitude:

Operating: Sea level to 10,000 ft. Storage: Sea level to 40,000 ft.

#### Relative Humidity (non-condensing)

| 0°C to +10°C:   | not controlled. |

|-----------------|-----------------|

| +11°C to +30°C: | 95 æ5% RH max.  |

| +31°C to +40°C: | 75 æ5% RH max.  |

| +41°C to +50°C: | 45 æ5% RH max.  |

#### 1.3.5 Size

Dimensions: Single slot, "C" size VXI module. (30 x 260 x 350 mm). Weight: <1.90 kg (4.19 lb.).

#### 1.3.6 **Power**

Total:<60 Watts

| Voltage | Peak Current | Dynamic Current |

|---------|--------------|-----------------|

| +5 Vdc  | 11.5A        | 1.5A            |

#### 1.3.7 Cooling Requirements

For 10 C degree rise 5.0 l/s, 0.5 mm H20

#### 1.4 Technical Specifications

This section describes the timing specifications for the BE-64. Unless otherwise noted, these timing specifications are valid in all cells of the timing set.

These specifications were obtained from a test fixture at the end of one foot ~100 ohm ribbon cables. If cables of a different length are used, then that difference must be taken into account. The rule of thumb for signal delay in cable is 1.7ns per foot.

#### 1.4.1 BE-64 Timing Set Specifications

The timing set specifications are in reference to the timing set cells. The timing set cells are defined by the TSOUT(1-8) signals measured on the UUT. See section 1.4.1.1.

#### 1.4.1.1 Clock Reference Timing

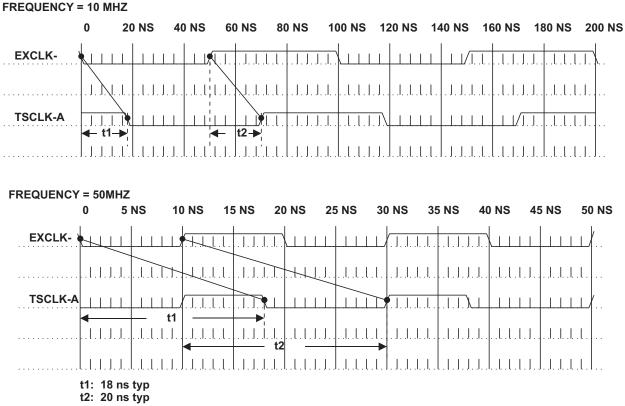

The source of the clock signal for the BE-64 consists of either an internal clock (TSCLK-A) or a user supplied external clock (EXCLK-, 50 MHz max.). Figure 1-1 illustrates the timing relationship between the two clocks when EXCLK- is used.

FIGURE 1-1 TSCLK-A IN REFERENCE TO EXCLK-

The timing set cells are defined by the TSOUT(1-8) signals measured on the UUT. Figure 1-3 illustrates

the TSOUT(1-8) signals with respect to TSCLK-A. Also, the relationship between the TSOUT signals is illustrated.

FIGURE 1-3 TSOUT(1-8) SIGNALS WITH RESPECT TO TSCLK-A

#### 1.4.1.2 Input Timing Set Signals

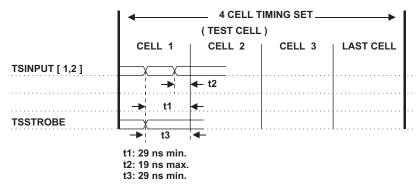

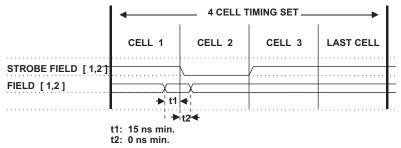

Figure 1-2 illustrates the timing specifications for the test input (handshake) signals. When using TSINPUT1 or TSINPUT2 the BE-64 will not enter a WAIT state if the respective signal is asserted t1 or greater prior to the beginning of the test cell and is not removed t2 or less prior to the beginning of the test cell.

When using TSSTROBE the BE-64 will not enter a WAIT state if the transition occurs t3 or greater prior to the beginning of the test cell. TSSTROBE test is invalid during the last cell.

For PCB REV. N/C the last cell cannot be used as a TSINPUT test cell. For PCB REV. A the last cell can be used as a TSINPUT test cell.

FIGURE 1-2 INPUT TIMING SET SIGNALS

#### 1.4.2 BE-64 Field Channel Specifications

The field channel specifications are in reference to the timing set cells. See section 1.4.1.1. Both fields are identical and independent. Only the address in the 32K memory is common between them.

Each field can have the direction set to input, output, or be controlled externally. When the direction is set to input, the input strobe can be controlled either internally or externally. When the direction is set to output, the output can be either registered or non-registered and the enable and strobe can be controlled either internally or externally.

#### 1.4.2.1 Non-registered Output Timing

In this section the direction of the field is set to output and is non-registered.

Figure 1-5 illustrates the time that data becomes valid when the output is continuously enabled. The

enable control may be either internal or external. Also, the relationship between the data channels is illustrated.

| SELECTION | OUTPUT<br>REGISTER |    | OUTPUT<br>CONTROL      | INPUT STROBE           |

|-----------|--------------------|----|------------------------|------------------------|

| INPUT     | N/A                |    | N/A                    | INTERNAL /<br>EXTERNAL |

| OUTPUT    | YES                | NO | INTERNAL /<br>EXTERNAL | N/A                    |

| EXTERNAL  | YES / NO           |    | INTERNAL /<br>EXTERNAL | INTERNAL /<br>EXTERNAL |

FIGURE 1-5 DATA VALID, CONTINUOUSLY ENABLED

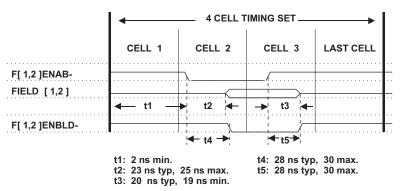

Figure 1-4 illustrates the time that data is valid when the enable is controlled internally. Due to signal delays, this timing specification does not apply to cell 1. Also, the time for F[1,2]ENBLD- to be asserted is illustrated.

| SELECTION | OUTPUT<br>REGISTER |    | OUTPUT<br>CONTROL      | INPUT STROBE           |

|-----------|--------------------|----|------------------------|------------------------|

| INPUT     | N/A                |    | N/A                    | INTERNAL /<br>EXTERNAL |

| OUTPUT    | YES                | NO | INTERNAL<br>EXTERNAL   | N/A                    |

| EXTERNAL  | YES / NO           |    | INTERNAL /<br>EXTERNAL | INTERNAL /<br>EXTERNAL |

FIGURE 1-4 DATA VALID/INVALID, INTERNALLY ENABLED

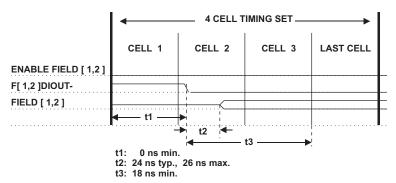

Figure 1-7 illustrates the time that data is valid when the enable is controlled externally. Due to signal delays, the timing specification for when data becomes valid (t2) only applies if the restriction on the enable signal with respect to the beginning of cell 1 (t1) is met. Should the external enable occur earlier,

then t2 will be reduced. The limit is t1 in figure 1-5. Also, the time for F[1,2]ENBLD- to be asserted is illustrated.

| SELECTION | OUTPUT<br>REGISTER |    | OUTPUT<br>CONTROL      | INPUT STROBE           |

|-----------|--------------------|----|------------------------|------------------------|

| INPUT     | N/A                |    | N/A                    | INTERNAL /<br>EXTERNAL |

| OUTPUT    | YES                | NO | INTERNAL<br>EXTERNAL   | N/A                    |

| EXTERNAL  | YES / NO           |    | INTERNAL /<br>EXTERNAL | INTERNAL /<br>EXTERNAL |

FIGURE 1-7 DATA VALID/INVALID, EXTERNALLY ENABLED

#### 1.4.2.2 Registered Output Timing

In this section the direction of the field is set to output and is registered.

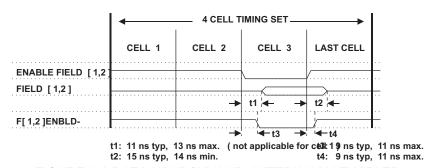

Figure 1-6 illustrates the time that data is valid when the enable is controlled internally and the internal strobe has already occurred. Due to signal delays, the internal strobe must not occur in cell 1.

| SELECTION | OUTPUT<br>REGISTER |  | OUTPUT<br>CONTROL | INPUT STROBE           |

|-----------|--------------------|--|-------------------|------------------------|

| INPUT     | N/A                |  | N/A               | INTERNAL /<br>EXTERNAL |

| ОИТРИТ    | YES NO             |  | INTERNAL          | N/A                    |

|           |                    |  | EXTERNAL          | 14,71                  |

| EXTERNAL  | YES / NO           |  | INTERNAL /        | INTERNAL /             |

|           |                    |  | EXTERNAL          | EXTERNAL               |

FIGURE 1-6 DATA VALID/INVALID, INTERNALLY ENABLED

Figure 1-9 illustrates the time that data becomes valid after the internally controlled strobe occurs and the

internal enable has already occurred. Due to signal delays, this timing specification does not apply to cell 1.

| SELECTION | OUTPUT<br>REGISTER |  | OUTPUT<br>CONTROL      | INPUT STROBE           |

|-----------|--------------------|--|------------------------|------------------------|

| INPUT     | N/A                |  | N/A                    | INTERNAL /<br>EXTERNAL |

| ОИТРИТ    | YES NO             |  | INTERNAL               | N/A                    |

|           |                    |  | EXTERNAL               | 1,7,1                  |

| EXTERNAL  | YES / NO           |  | INTERNAL /<br>EXTERNAL | INTERNAL /<br>EXTERNAL |

FIGURE 1-9 DATA VALID, INTERNALLY STROBED

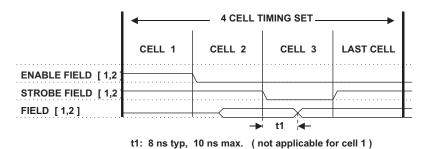

Figure 1-8 illustrates the time that data becomes valid when the strobe is controlled externally and the external enable has already occurred. Due to signal delays, the timing specification for when data becomes valid (t2) only applies if the restriction on the strobe signal with respect to the beginning of cell 1 (t1) is met. The external strobe must not occur prior to t1. Figure 1-8 also illustrates the time that data becomes invalid when the field is externally disabled.

| SELECTION | OUTPUT<br>REGISTER |    | OUTPUT<br>CONTROL      | INPUT STROBE           |

|-----------|--------------------|----|------------------------|------------------------|

| INPUT     | N/A                |    | N/A                    | INTERNAL /<br>EXTERNAL |

| ОИТРИТ    | YES                | NO | INTERNAL<br>EXTERNAL   | N/A                    |

| EXTERNAL  | YES / NO           |    | INTERNAL /<br>EXTERNAL | INTERNAL /<br>EXTERNAL |

FIGURE 1-8 DATA VALID, EXTERNALLY STROBED

#### 1.4.2.3 Input Timing

In this section the direction of the field is set to input. When set to input, the field is always registered and enabled.

Figure 1-11 illustrates the data set-up and hold times for the internally controlled strobe.

| SELECTION | OUTPUT<br>REGISTER | OUTPUT<br>CONTROL      | INPUT STROBE           |

|-----------|--------------------|------------------------|------------------------|

| INPUT     | N/A                | N/A                    | INTERNAL<br>EXTERNAL   |

| OUTPUT    | YES / NO           | INTERNAL /<br>EXTERNAL | N/A                    |

| EXTERNAL  | YES / NO           | INTERNAL /<br>EXTERNAL | INTERNAL /<br>EXTERNAL |

FIGURE 1-11 DATA SET-UP AND HOLD, INTERNALLY STROBED

Figure 1-10 illustrates the data set-up and hold times for the externally controlled strobe. There is also a restriction as to how close the external strobe can occur prior to the end of the last cell.

| SELECTION | OUTPUT<br>REGISTER | OUTPUT<br>CONTROL      | INPUT STROBE           |

|-----------|--------------------|------------------------|------------------------|

| INPUT     | N/A                | N/A                    | INTERNAL /<br>EXTERNAL |

| OUTPUT    | YES / NO           | INTERNAL /<br>EXTERNAL | N/A                    |

| EXTERNAL  | YES / NO           | INTERNAL /<br>EXTERNAL | INTERNAL /<br>EXTERNAL |

FIGURE 1-10 EXTERNAL DIRECTION TO INPUT

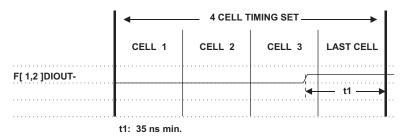

#### 1.4.2.4 Bidirectional Timing

In this section the direction of the field is externally controlled. To ensure that the field functions correctly as an input or output, it is recommended that the external direction signal remain true during the entire timing set, especially in the last cell.

Should the external direction signal change state during the timing set, then figure 1-13 illustrates the time that data becomes valid when the external direction is set to output and the field is continuously enabled.

| SELECTION | OUTPUT<br>REGISTER | OUTPUT<br>CONTROL      | INPUT STROBE           |

|-----------|--------------------|------------------------|------------------------|

| INPUT     | N/A                | N/A                    | INTERNAL /<br>EXTERNAL |

| OUTPUT    | YES / NO           | INTERNAL /<br>EXTERNAL | N/A                    |

| EXTERNAL  | YES / NO           | INTERNAL /<br>EXTERNAL | INTERNAL /<br>EXTERNAL |

FIGURE 1-13 EXTERNAL DIRECTION SET TO OUTPUT

To ensure that the correct word of data becomes available at the output, there is a restriction as to how close the external direction signal can change prior to the beginning of the last cell.

Figure 1-12 illustrates the restriction on the external direction signal in order to set the field to input

| SELECTION | OUTPUT<br>REGISTER | OUTPUT<br>CONTROL      | INPUT STROBE           |

|-----------|--------------------|------------------------|------------------------|

| INPUT     | N/A                | N/A                    | INTERNAL<br>EXTERNAL   |

| OUTPUT    | YES / NO           | INTERNAL /<br>EXTERNAL | N/A                    |

| EXTERNAL  | YES / NO           | INTERNAL /<br>EXTERNAL | INTERNAL /<br>EXTERNAL |

FIGURE 1-12 DATA SET-UP AND HOLD, EXTERNALLY STROBED

To ensure that the data is stored in the correct memory location, the external direction signal must be set to input at least t1 prior to the end of the last cell. See section 1.4.2.3 for relevant data set-up and hold times.

### 1.5 BE-64 Drive Specifications

Appendix G includes the type of device used as a driver as well as any termination for all BE-64 signals.

## 2 PREPARATION

#### 2.1 RECEIVING INSPECTION

Check the shipment at the time of delivery and inspect each box for damage. Describe any box damage and list any shortages on the delivery invoice.

#### 2.1.1 Unpacking Instructions

- 1. **Unpack the boxes.** Unpack the boxes in a clean and dry environment. Save all the packing material in case the instrument must be returned for repair.

- 2. **Inspect the shipment for damage.** Inspect the equipment carefully for any signs of mechanical damage regardless of the condition of the shipping boxes.

- 3. **If necessary, file a claim.** In the case of mechanical damage, call the shipper immediately and start the claim process.

- 4. Call Customer Service representative (800-722-2528) if the shipment arrived damaged. Please be prepared to provide a detailed damage report.

#### 2.1.2 Returning Equipment

Follow these steps when you return equipment to Talon:

- 1. **Save the packing material.** Always return equipment in its original packing material and boxes. If you use inadequate material, you'll be responsible for any shipping damage repair as carriers won't accept responsibility on incorrectly packed equipment.

- 1. Call (800-722-2528) for a Return Material Authorization number (RMA). The Customer Service representative will ask for your name, telephone number, company name, equipment type, model number, serial number, and a description of your problem.

- 3. Pack and ship the equipment to:

Talon Instruments 4 Goodyear Irvine, CA 92618

#### 2.2 PREPARATION FOR STORAGE OR SHIPMENT

#### 2.2.1 Packaging

If at all possible, always use the original shipping container. Use a double-walled cardboard shipping container. Protect all sides, including the top and bottom, with shock absorbing material (minimum of 1 inch thick material) to prevent movement of the BE-64 within the container. Seal the shipping container with approved sealing tape. Mark "FRAGILE" on all sides, top, and bottom of the shipping container.

#### 2.2.2 Storage

The BE-64 should be stored in a clean, dry environment. In high humidity environments, protect the BE-64 from temperature variations that could cause internal condensation. The following environmental conditions apply to both shipping and storage:

Temperature -40°C to +71°C

Relative Humidity not controlled, non-condensing

Altitude <40000 ft. (12192 m)

Vibration <2g Shock <40g

#### 2.3 PREPARATION FOR USE

Paragraph 2.3 covers the following topics:

Logical Address Selection

- Rear Panel Connectors

- Jumper Configuration

- Cables

- Installation

#### 2.3.1 Logical Address Selection

The VXI chassis Resource Manager identifies units in the system by the unit's logical address. The VXI logical address can range from 0 to 255. The exceptions are addresses 0 and 255. Address 0 is reserved for the Resource Manager. Address 255 is an invalid address for the BE-64.

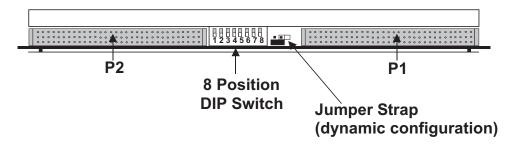

The logical address of the BE-64 can be statically or dynamically configured. A jumper strap, as seen from the rear panel (FIGURE 2-1), is installed across jumper points E42 and E43 (E50 and E51 rev NC PCB) for static configuration. The jumper strap is removed for dynamic configuration. Talon ships the BE-64 in the dynamic configuration. The jumper strap, however, is installed on only one jumper point, as seen in FIGURE 2-1 (not connecting E42 and E43).

With the jumper strap installed for static configuration, the BE-64's logical address can be changed by setting the eight position DIP switch (FIGURE 2-1). The BE-64 uses binary values ( $2^0$  to  $2^7$ ) to set the address. The up position (as viewed in FIGURE 2-1) represents a logical 1. The down position represents a logical 0. Switch position number one is the least significant bit of the address.

FIGURE 2-1 REAR PANEL

#### 2.3.2 Rear Panel Connectors

Two multi-pin rear panel connectors, P1 and P2, connect the BE-64 to the VXI chassis. These connectors provide power supplies, digital interfacing, and the backplane signal lines used by the BE-64.

#### 2.3.3 Jumper Configurations

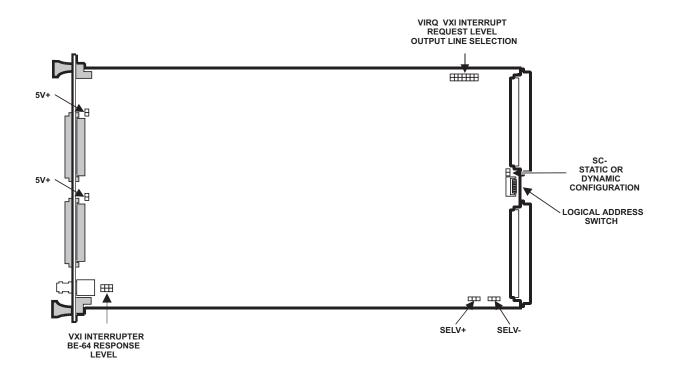

See TABLE 2-1 for all jumper settings. See FIGURE 2-2 for the location of all the jumper points. All jumper points are located on the CPU card (bottom board). The Bus Emulator card (top board) must be carefully removed if the jumper configuration, other than the interrupt settings, is to be checked or changed. The interrupt settings are right angle jumpers accessible from the side.

| SIGNAL<br>NAME | "E"<br>LOCATION      | IF SHIPPED INSTALLED | FUNCTION                                                                                                         |

|----------------|----------------------|----------------------|------------------------------------------------------------------------------------------------------------------|

| 5V+            | E50 E51<br>(E53 E54) | NO                   | Connects +5V from VXI backplane to front connectors J3 and J4.                                                   |

| 5V+            | E26 E27<br>(E28 E29) | NO                   | Connects +5V from VXI backplane to front connector J1.                                                           |

| SELV+ (+24V)   | E61 E62<br>(E66 E67) | NO                   | Connects +24V from VXI backplane to front connector J3.                                                          |

| SELV+ (+12V)   | E60 E61<br>(E65 E66) | NO                   | Connects +12V from VXI backplane to front connector J3.                                                          |

| SELV- (-24v))  | E64 E65<br>(E69 E70) | NO                   | Connects -24V from VXI backplane to front connector J3.                                                          |

| SELV- (-12V)   | E63 E64<br>(E68 E69) | NO                   | Connects -12V from VXI backplane to front connector J3.                                                          |

| SC-            | E43 E42<br>(E50 E51) | NO<br>OR<br>OFFSET   | Static configuration if jumper strapped, then logical DIP switch is used. Dynamic configuration if not strapped. |

| SIGNAL<br>NAME | "E"<br>LOCATION        | IF SHIPPED<br>INSTALLED | FUNCTION                                                                                                               |

|----------------|------------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------|

| LEV1           | E57 E54<br>(E59 E62)   | NO                      | VXI interrupt request response level. Binary encoded.                                                                  |

| LEV2           | E58 E55<br>(E60 E63)   | YES                     |                                                                                                                        |

| LEV3           | E59 E56<br>(E61 E64)   | YES                     |                                                                                                                        |

| VIRQ1-         | E12 E19<br>(E14 E21)   | YES                     | VXI interrupt request to VXI interrupt request level output selection. One selection made by the user. Must also match |

| VIRQ2-         | E13 E20<br>(E15 E22)   | NO                      | binary encoded level (LEV_) jumper selections.                                                                         |

| VIRQ3-         | E1 4 E21<br>(E1 6 E23) | NO                      |                                                                                                                        |

| VIRQ4-         | E15 E22<br>(E17 E24)   | NO                      |                                                                                                                        |

| VIRQ5-         | E16 E23<br>(E18 E25)   | NO                      |                                                                                                                        |

| VIRQ6-         | E17 E24<br>(E19 E26)   | NO                      |                                                                                                                        |

| VIRQ7-         | E18 E25<br>(E20 E27)   | NO                      |                                                                                                                        |

#### **2.3.4 Cables**

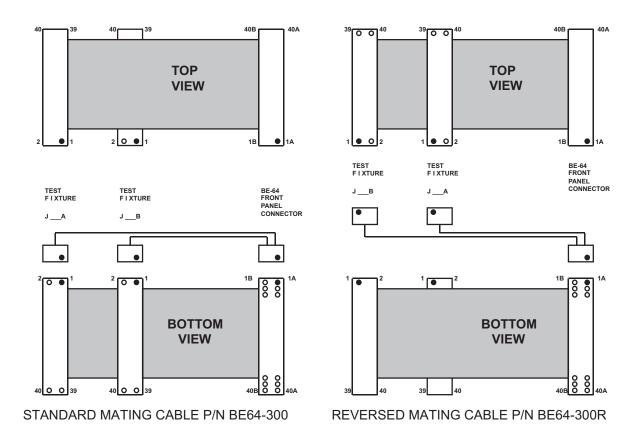

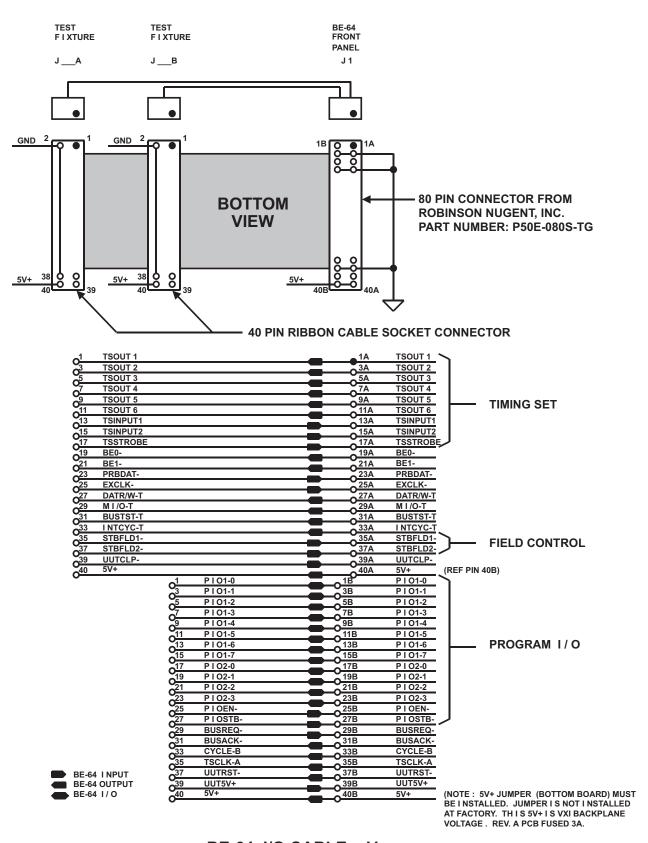

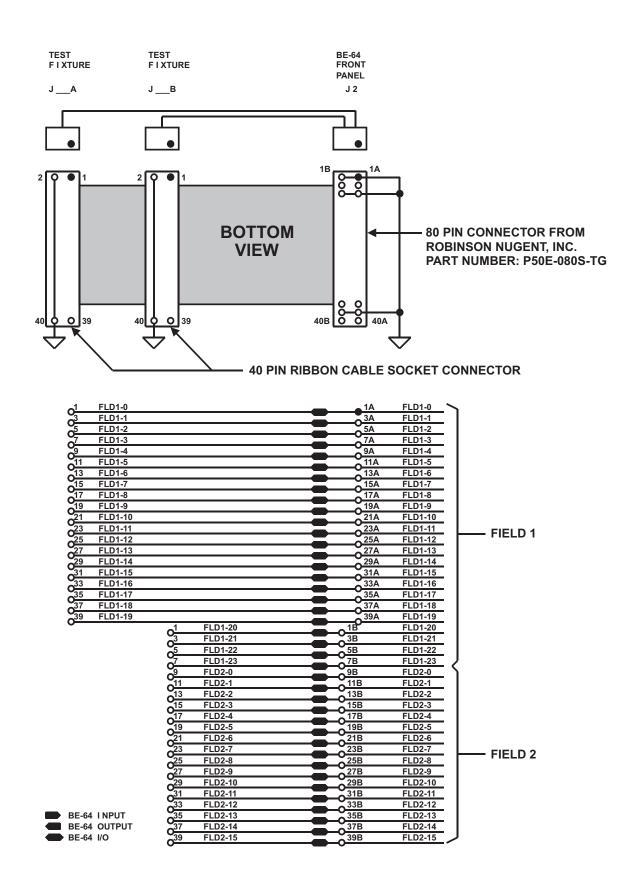

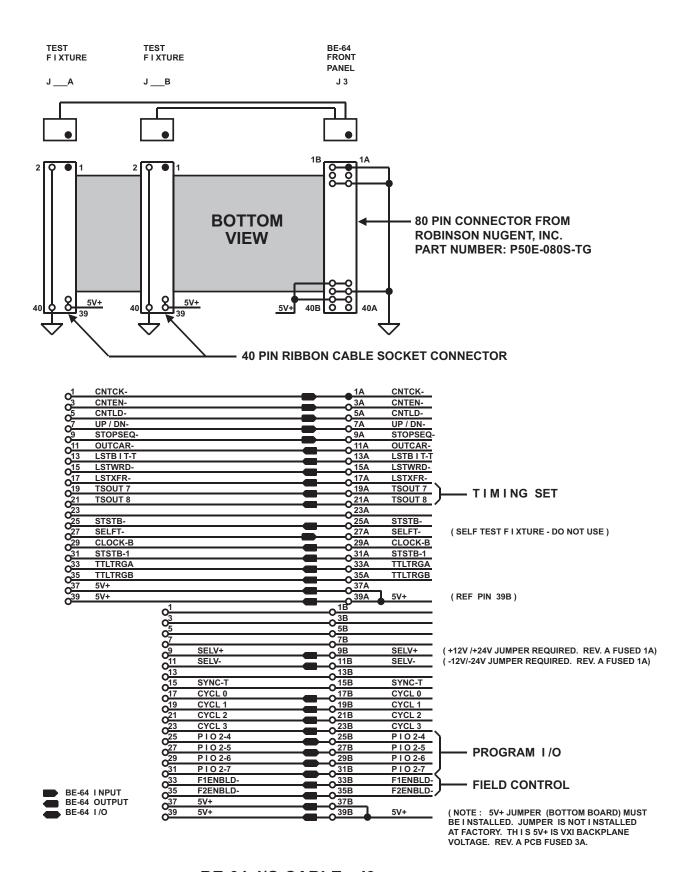

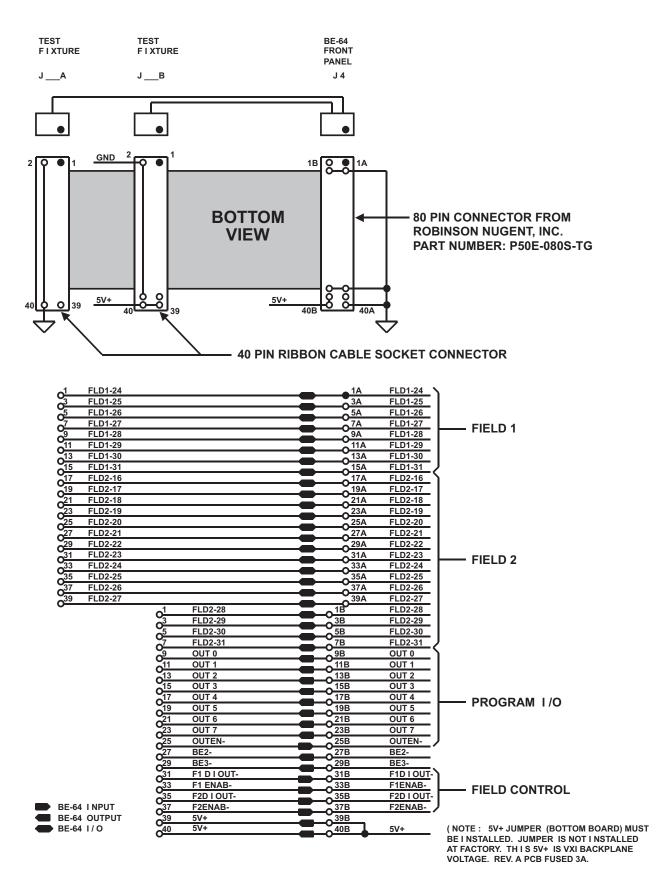

Since the user will require customized cables for the front panel connectors (J1-J4), Appendix E (J1-J4 Pinouts) has been provided. Appendix F includes a worksheet for each connector to be copied and filled in with the pinout of the user's custom built cables. Mating connectors for J1-J4 can be obtained from

TABLE 2-1 BOTTOM BOARD REV A AND (REV NC) JUMPER SETTINGS

FIGURE 2-2 LOCATION OF JUMPER POINTS (BOTTOM BOARD)

Robinson Nugent, Inc. (part number: P50E-080S-TG).

Appendix E contains examples and pinouts of typical cables using standard 40 pin connectors to mate with the UUT. These cables can be ordered from Talon (part number: BE64/300).

The cable assembly includes the 80 pin mating connector, three feet of 28 AWG ribbon cable and four forty pin headers (two spare and two crimped).

#### 2.4 INSTALLATION

The BE-64 must be installed in a VXI mainframe in any slot except slot 0 (zero), which is reserved for the Resource Manager. Always check P1 and P2 for bent pins prior to installation. When inserting the BE-64 into the mainframe, it should be gently rocked back and forth to seat the connectors into the backplane receptacles.

#### 2.4.1 Initial Power-On

With the BE-64 properly installed in a VXI chassis, turn the chassis power on. The BE-64 will immediately conduct a self-test which tests memory, registers, communication with the host, etc. (Note: a self-test adapter must be connected to the front connectors to test the full integrity of the drivers and receivers). The red FAIL indicator will come on and the SYSFAIL- line on the VXI backplane will be driven true. The other indicators may or may not flash during the self-test. After about three seconds, if the BE-64 passes the self-test, then the FAIL indicator will go off, all the other indicators will be off, and the SYSFAIL- line will no longer be driven by the BE-64. The BE-64 is now ready for use.

If the BE-64 fails the self test, then the FAIL indicator will stay on or flash and the SYSFAIL- line will continue to be driven. Should this happen, turn the chassis power off, make certain the BE-64 is properly installed, and turn the chassis power back on. Should the BE-64 continue to fail, then call the Customer Service representative (800-722-2528) for assistance.

An optional self test fixture (talon part number BE64/201) provides an extended test of the BE-64's front panel I/O signals.

# 3 OVERVIEW

#### 3.1 INTRODUCTION

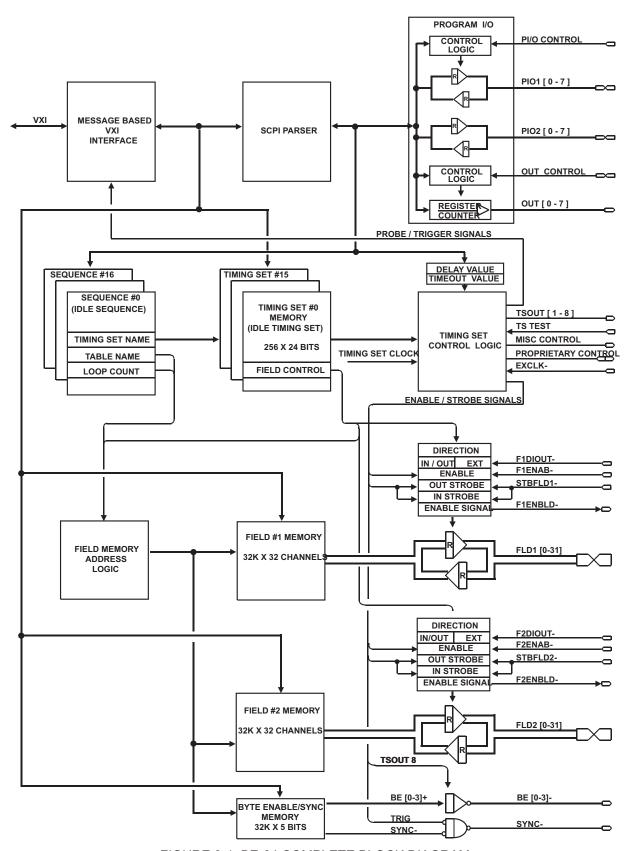

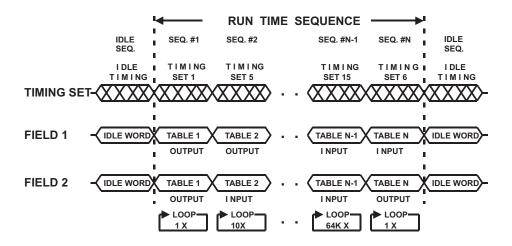

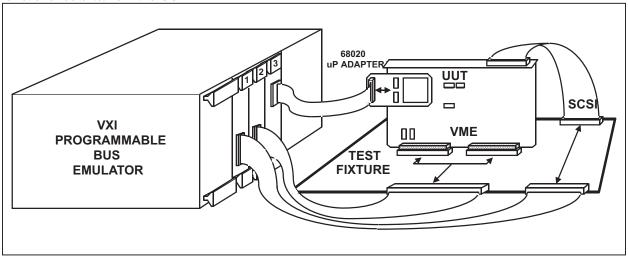

The BE-64 can be thought of as a word generator, a timing generator, and a logic recorder all combined into a single "C"+ size VXI bus emulator card. Figure 3-1 is the block diagram of the BE-64. It must be understood that, in the BE-64, bus emulation is controlled by the timing sets. Each timing set is an executable cycle which simulates a bus cycle. The timing sets, in fact, define the characteristics of the bus to the BE-64. Appendix C will help in understanding bus emulation.

#### 3.2 SYSTEM RESOURCES

The BE-64 is a 68010 microprocessor controlled VXI message based servant. The 68010 microprocessor system includes 128K of ROM and 64K of RAM. An additional 128K of ROM and 64K of RAM are available for MACRO programming of the BE-64. The operating system is multi-tasking which, in addition to performing system I/O and resource management, performs the following functions:

- Performs a system power-up self-test.

- Receives, parses and executes the SCPI commands.

- Processes the command data and converts them into an appropriate digital format compatible with the bus emulator logic.

- Executes built in functions such as RAM and ROM tests.

- Calculates CRC'S on field memories such that a "Learn UUT" function can be executed.

- Performs a table compare function on the field memories.

The MACRO programming allows the user to customize the BE-64 with unique timing sets and commands that can be executed by standard SCPI commands.

In order to speed up the access of the BE-64's field and timing data, these memories have been assigned VXI A24 addresses and can be accessed directly via the VXI controller.

The BE-64 is also capable of generating VXI bus interrupts for any of the events in the status register. The BE-64 is shipped from the factory with VXI IRQ1 enabled. Any of the seven VXI IRQ lines can be selected via hardware jumper.

FIGURE 3-1 BE-64 COMPLETE BLOCK DIAGRAM

#### 3.3 CONNECTORS AND INDICATORS

The BE-64 has four LED indicators, four 80 pin connectors, and one BNC connector. The front panel connectors and indicators are shown in figure 3-2 with the following descriptions:

- FAIL/ID. The FAIL/ID indicator is a dual red/green LED. The red LED illuminates during the power-up self-test and stays on or flashes if a system failure is detected. Otherwise, it is turned off. The green LED illuminates whenever the MODULE ID line for this board, on the backplane, is active. An amber color is displayed if both LEDs are illuminated at the same time.

- 2. BUSY. The BUSY indicator is a red LED which illuminates when the BE-64 is executing a non-idle timing sequence. Otherwise, it is off.

- 3. WAIT. The WAIT indicator is a red LED which illuminates when the BE-64 is in a "WAIT" state. The BE-64 enters a "WAIT" state during a "test cell" (TSINPUT1, TSINPUT2, TSSTROBE), a "delay cell", or when the bus acknowledge line (BUSACK-) is asserted by the BE-64 in response to a bus request (BUSREQ-) from the UUT. Otherwise, it is off.

- 4. TIMEOUT. The TIMEOUT indicator is a red LED which illuminates if the programmable timeout function is enabled and a timeout condition has occurred. Otherwise, it is off.

- 5. J1. The J1 connector provides the signals necessary to interface with the UUT. See Appendix G for a complete description of these signals. See Appendix E for a complete pinout of the J1 connector.

- 6. J2. The J2 connector provides the signals necessary to interface with the UUT. See Appendix G for a complete description of these signals. See Appendix E for a complete pinout of the J2 connector.

- 7. J3. The J3 connector provides the signals necessary to interface with the UUT. See Appendix G for a complete description of these signals. See Appendix E for a complete pinout of the J3 connector.

- 8. J4. The J4 connector provides the signals necessary to interface with the UUT. See Appendix G for a complete description of these signals. See Appendix E for a complete pinout of the J4 connector.

- SYNC. The SYNC BNC provides an output signal which is the user programmed TRIGGER signal, of the Timing Set, gated with the internal memory table sync signal. SYNC is commonly used to trigger a scope.

FIGURE 3-2 FRONT PANEL CONNECTORS AND INDICATORS

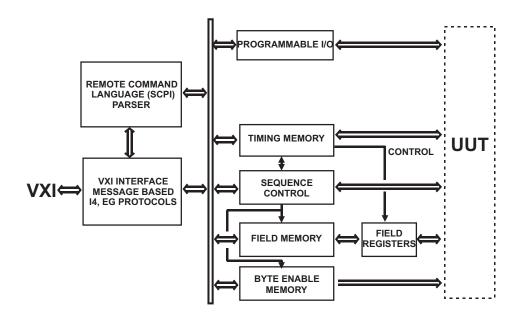

#### 3.4 BE-64 FUNCTIONAL OVERVIEW

The BE-64, as illustrated in figure 3-3, can be separated into seven functional blocks listed below. Each block will be described in the following sections.

FIGURE 3-3 SIMPLIFIED BLOCK DIAGRAM

- VXI Interface.

- Remote Command Language Parser.

- · Field Memory and Registers.

- · Timing Memory.

- Sequence Control.

- Programmable I/O.

- Byte Enable Memory.

#### 3.4.1 VXI Interface

The BE-64 is a message based servant that supports the IEEE 488.2 Instrument (I4) and Event Generator (EG) protocol.

Messages and commands are sent to the BE-64 via word serial protocol. In addition, the timing and field memories are assigned A24 VXI addresses so that the VXI controller can access the memory faster using direct memory access.

#### 3.4.2 Remote Command Language Parser

The BE-64 conforms to the SCPI (Standard Commands for Programmable Instruments) version 1991.0. See Appendix A for an introduction to SCPI. See Section 5 for a description of the SCPI commands used by the BE-64.

#### 3.4.3 Field Memory and Registers

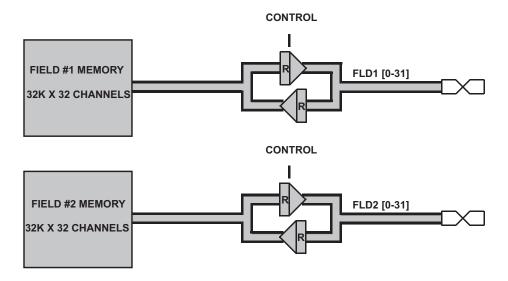

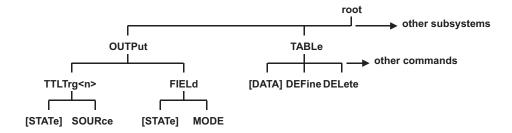

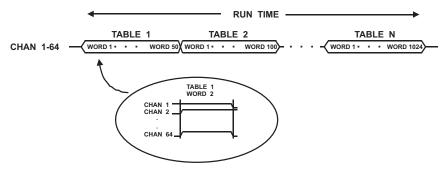

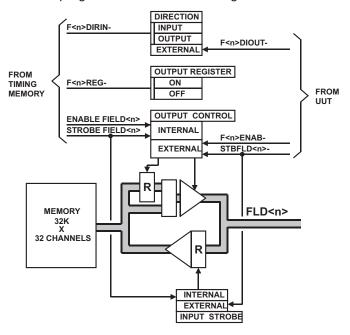

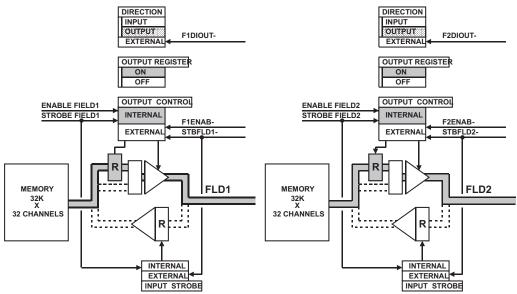

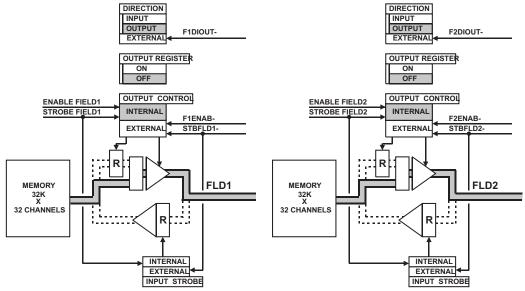

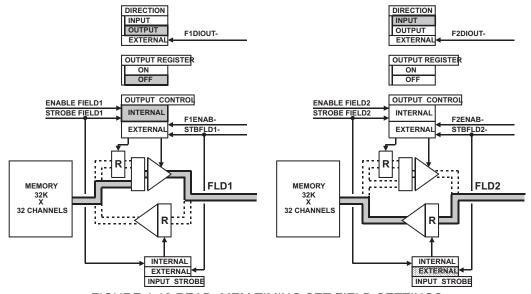

The 64 X 32K field memory of the BE-64 is connected to the UUT via field registers as depicted in figure 3-4.

FIGURE 3-4 FIELD MEMORY/REGISTER BLOCK DIAGRAM

The field memory is allocated in groupings called tables. Tables are used in the BE-64 to store stimulus or response data from the UUT. Each table is dedicated to a specific UUT operation. Up to 256 tables may be defined. Additional tables are allocated depending on the availability of memory. The length of each table may be from 1 word to the full 32K of memory. The maximum data rate of the field memory is 25 MHz.

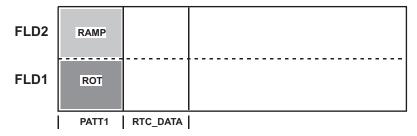

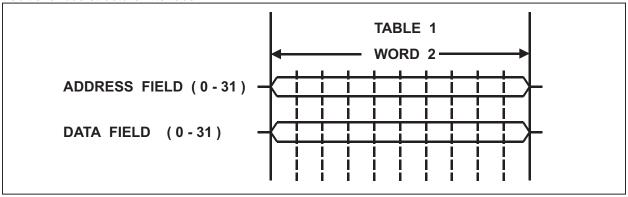

The field registers are separated into two groups called FLD1 and FLD2. The two fields are identical, yet independently controlled. For example, one field could be in the output mode while the other is in the input mode. The two fields are used to emulate synchronous interfaces such as the address and data bus. The field registers are programmed by the timing memory. The timing memory specifies the following settings of the field registers:

- Field Direction: The field direction can be set to input, output or external control. External field control allows the field to be bi-directional.

- Output Register: For fields programmed as output or external, the output register can be turned on or off. Turning the output register off puts the field register in a transparent mode, i.e., field memory is passed immediately through the register.

- Output Control: For fields programmed as output or external, the strobe and enable signal source can be internal or external. Internal signals are programmed in the timing memory.

- Input Control: For fields programmed as input or external the strobe signal source can be internal or external. The internal strobe is programmed in the timing memory.

Refer to section 3.4.4 for a complete description of the timing memory.

#### 3.4.4 Timing Memory

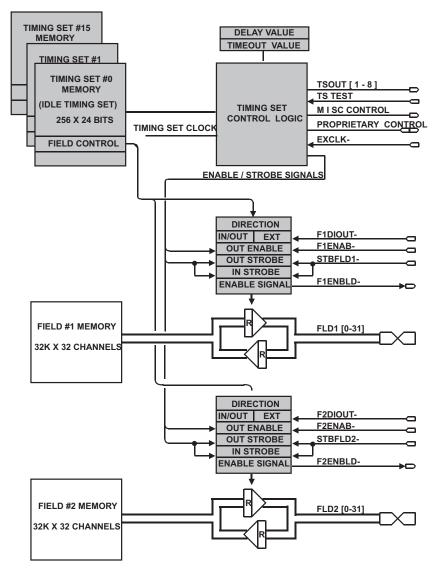

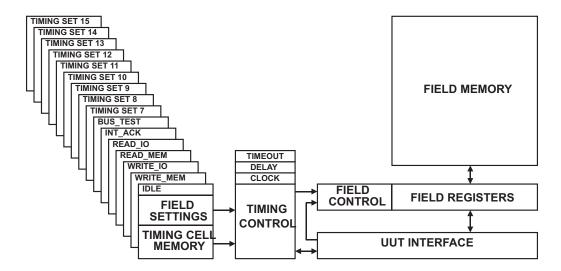

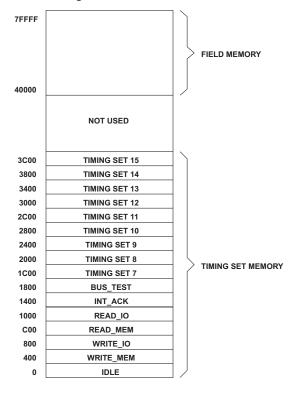

The Timing Memory of the BE-64 is split into 16 separate timing memories called timing sets as depicted in figure 3-5.

FIGURE 3-5 TIMING MEMORY BLOCK DIAGRAM

The first seven timing sets have pre-defined names and functions as described below:

- 1. IDLE: Used in the idle sequence, refer to section 3.4.5.1.

- 2. WRITE\_MEM: Used for RAM test functions, Drives front panel signals DATR/W-T low and MI/O-T high.

- 3. WRITE\_IO: Drives front panel signals DATR/W-T and MI/O-T low.

- 4. READ\_MEM: Used for RAM and ROM test functions, Drives front panel signals DATR/W-T and MI/O-T high.

- 5. READ IO: Drives front panel signals DATR/W-T high and MI/O-T low.

- 6. INT ACK: Drives front panel signal INTCYC-T low.

- 7. BUS\_TEST: Used for BUS test function, Drives front panel signal BUSTST-T low.

The timing set memory is connected to the UUT via the timing set control logic. The control logic contains the settings for the timing set clock as well as the delay and timeout values. The timing set control logic also contains Miscellaneous Control Signals, Proprietary Control Signals, as well as the external clock input signal. Descriptions of these signals can be found in Appendix G.

Each timing set can be viewed as a structure which defines the following data:

- Field Register Settings.

- 256 timing states called 'cells'.

## 3.4.4.1 Field Register Settings

The Field Register settings define how the 64 I/O field registers are configured. The field registers are configured in two separate groups of 32 channels each called fields. The following selections must be programmed for each field:

- · Field Direction.

- Output Mode.

- · Input Mode.

#### 3.4.4.1.1 Field Direction

Each timing set (1 of 16) specifies the field direction to be either input, output, or controlled externally (F1DIOUT-, F2DIOUT-), see figure 3-5. When configured to the output mode, the present word from the 32 bit x 32K memory is available for output to the 32 bit I/O field bus. When configured to the input mode, the present data on the 32 bit I/O field bus may be strobed into the input register and subsequently transferred to the field memory at the end of each timing set cycle.

#### 3.4.4.1.2 Output Mode

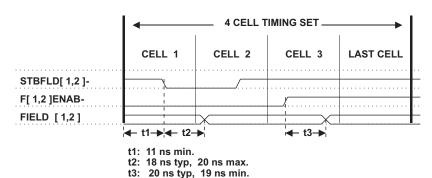

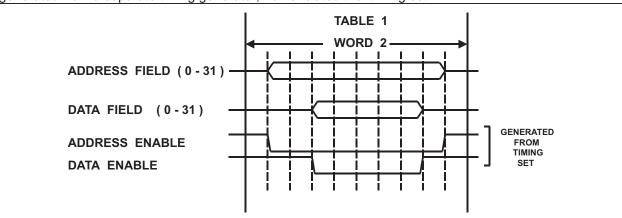

When the field is configured to the output mode, the timing set specifies whether or not it is registered. If it is registered, then a strobe signal is required to transfer the data from the field memory into the output register, see figure 3-5. The timing set specifies the strobe signal to be from either the timing set (STROBE FIELD1, STROBE FIELD2) or the external strobe line (STBFLD1-, STBFLD2-). If it is not registered, then the data is buffered directly from the field memory to the I/O field bus.

Both registered and non-registered configurations (output mode) require an enable signal, see figure 3-5. The timing set specifies the enable signal to be from either the timing set (ENABLE FIELD1, ENABLE FIELD2) or the external enable line (F1ENAB-, F2ENAB-). When disabled, the I/O field bus is in the high impedance state.

# 3.4.4.1.3 Input mode

If the field is configured to the input mode, then a strobe signal is required to transfer the data from the I/O field bus into the input register, see figure 3-5. The timing set specifies the strobe signal to be from either the timing set (STROBE FIELD1, STROBE FIELD2) or the external strobe line (STBFLD1-, STBFLD2-).

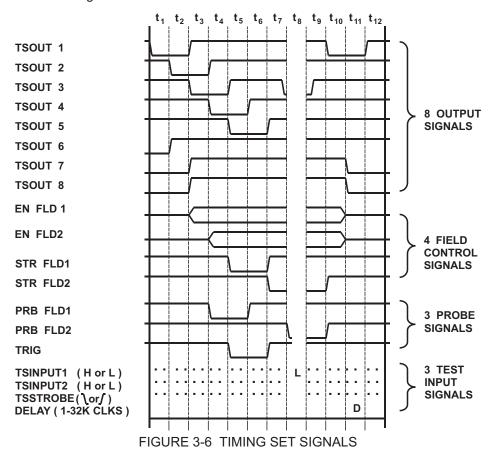

#### 3.4.4.2 Timing States/Cells

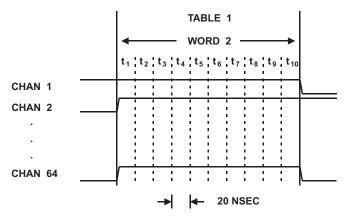

The 256 timing cells in each timing set represents a unique state in a timing cycle. The transition from cell to cell is made on the falling edge of the timing set clock, i.e., every cell is one period of the clock.

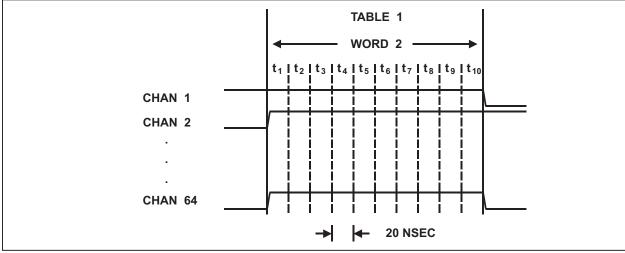

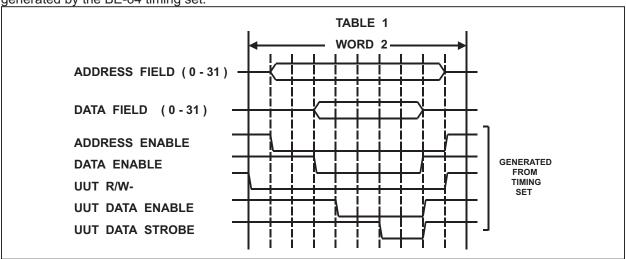

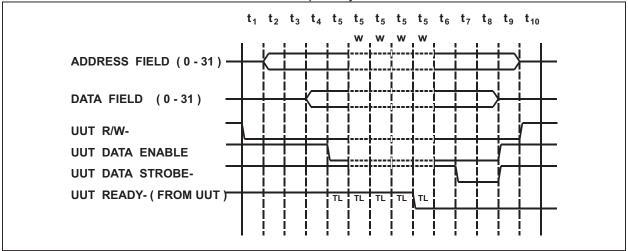

The maximum signal rate of the timing set clock is 50 MHz (20 nsec minimum cell width). Figure 3-6 is an example of a 12 cell timing set.

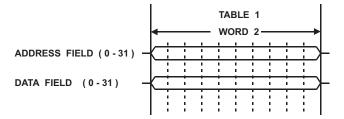

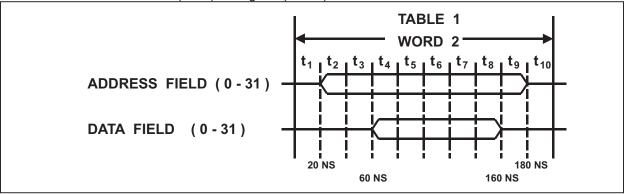

Each timing set can be programmed from 2 to 256 cells. The total number of cells must be an even number. Two of the timing cells (first cell and last cell) perform a special function. During the first cell, data from the field memory is enabled to the output field registers. During the last cell data from the input field registers is written to the field memory only if the field is set to input.

For each cell the following data must be programmed:

- 1. TTL level for the eight timing set outputs (TSOUT1 TSOUT8).

- 2. Internal Field Control settings for both fields.

- 3. Probe and trigger levels.

- 4. Test Input/Delay code.

#### 3.4.4.2.1 Timing Set TSOUT Signals.

The eight TSOUT output signals are general purpose programmable signals available for the UUT or test fixture interface. They can be programmed to a high or low level with 20 nsec resolution. The TSOUT signals are typically used to simulate signals such as address strobes, data strobes, read/write control, etc.

Additionally TSOUT8 is used as the internal enable for the byte enable memory outputs.

#### 3.4.4.2.2 Timing Set Field Control Signals

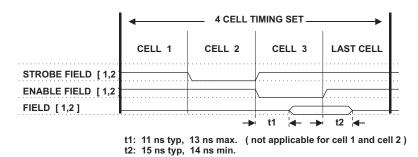

The two EN FLD signals are controls to the respective I/O field. When selected, and when the respective I/O field is in the output mode, the EN FLD signal sets the I/O field from the high impedance state to an active state.

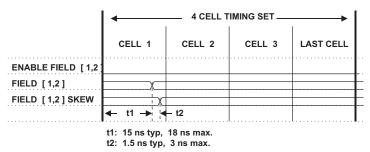

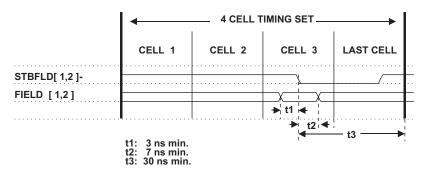

The two STR FLD signals are controls to the respective I/O field. When the I/O field is in the output registered mode, the STR FLD signal strobes the data from the field memory into the output register. The data transfer occurs on the positive to negative transition of the strobe signal. Since data from the field memory is not available until after the beginning of the timing set, the strobe signal must occur after the first cell (t1).

When the I/O field is in the input mode, the STR FLD signal strobes the data from the I/O field bus into the input register. The data transfer occurs on the positive to negative transition of the strobe signal. Since the data in the input register is transferred into the field memory during the last cell of the timing set the strobe signal must occur 20ns prior to the end of the last cell.

## 3.4.4.2.3 Timing Set Probe Signals

The two PRB FLD signals can be routed to one of the VXI TTLTRG lines, TTLTRG0 - TTLTRG3. The PRB FLD signals are typically used to trigger the UUT or other VXI instruments. The user should program these signals within the enable time of the respective EN FLD signal.

The TRIG signal is gated with the memory table sync signal. This combinatorial signal is available on the front panel through either the BNC (SYNC) or J3 pin 15B (Rev. A PCB only)and is typically used to trigger an oscilloscope. This signal can also be routed to one of the VXI TTLTRG lines, TTLTRG4 - TTLTRG7.

## 3.4.4.2.4 Timing Set Test/Delay Options